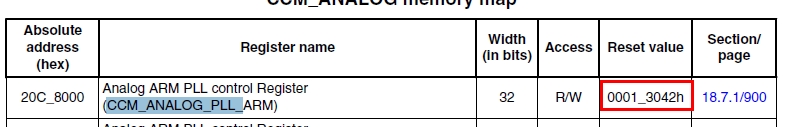

Imx6q는 기본값이 792MHz로 사용을 한다.

아래 공식에 대입하면

기본값이 0x00013042에서 하위 7bit 값이 div 값임.

0x42 == 10진수 66이 됨

792MHz = 24MHz * 66/2 입니다.

|

18.5.1.3.1 ARM PLL This PLL synthesizes a low jitter clock from a 24 MHz

reference clock. The clock output frequency for this PLL ranges from 650 MHz to 1.3 GHz.

The output frequency is selected by a 7-bit register field CCM_ANALOG_PLL_ARM[DIV_SELECT]. PLL output frequency = Fref * DIV_SEL/2

|

1.2GHz로 동작하기 위해서는 아래와 같이 수정하면 됩니다.

1200MHz = 24MHz * 100 / 2

CCM_ANALOG_PLL_ARM[DIV_SELECT] 값이 100이면 됩니다.

arch/arm/cpu/armv7/mx6/soc.c

|

void s_init(void) { struct mxc_ccm_reg *ccm = (struct mxc_ccm_reg *)CCM_BASE_ADDR; int is_6sx = is_cpu_type(MXC_CPU_MX6SX); u32 mask480; u32 mask528; u32 reg, periph1, periph2; //crazyboys

2016 0407 1.2Ghz writel(0x00013064,&ccm->analog_pll_sys); |

실행 결과

|

U-Boot 2014.04-08648-g9d7bf9b-dirty (Apr 07 2016 - 09:46:11)

CRZ freq=1200000000, reg=0 CPU: Freescale i.MX6Q rev1.5 at 1200 MHz CPU: Temperature 31 C, calibration data: 0x5514c469 Reset cause: POR Board: MX6-SabreSD I2C: ready DRAM: 2 GiB MMC: FSL_SDHC: 0, FSL_SDHC: 1, FSL_SDHC: 2 No panel detected: default to Hannstar-XGA Display: Hannstar-XGA (1024x768) In: serial Out: serial Err: serial unsupported boot devices check_and_clean: reg 0, flag_set 0 Fastboot: Normal flash target is MMC:2 Net: FEC [PRIME] Warning: failed to set MAC address

Normal Boot Hit any key to stop autoboot: 0 => => => => => => => => clock PLL_SYS 1200 MHz PLL_BUS 528 MHz PLL_OTG 480 MHz PLL_NET 50 MHz

IPG 66000 kHz UART 80000 kHz CSPI 60000 kHz AHB 132000 kHz AXI 264000 kHz DDR 528000 kHz USDHC1 198000 kHz USDHC2 198000 kHz USDHC3 198000 kHz USDHC4 198000 kHz EMI SLOW 132000 kHz IPG PERCLK 66000 kHz |

내용